- 您现在的位置:买卖IC网 > Sheet目录3841 > PIC16C63A-04I/SO (Microchip Technology)IC MCU OTP 4KX14 PWM 28SOIC

PIC16C63A/65B/73B/74B

DS30605C-page 10

2000 Microchip Technology Inc.

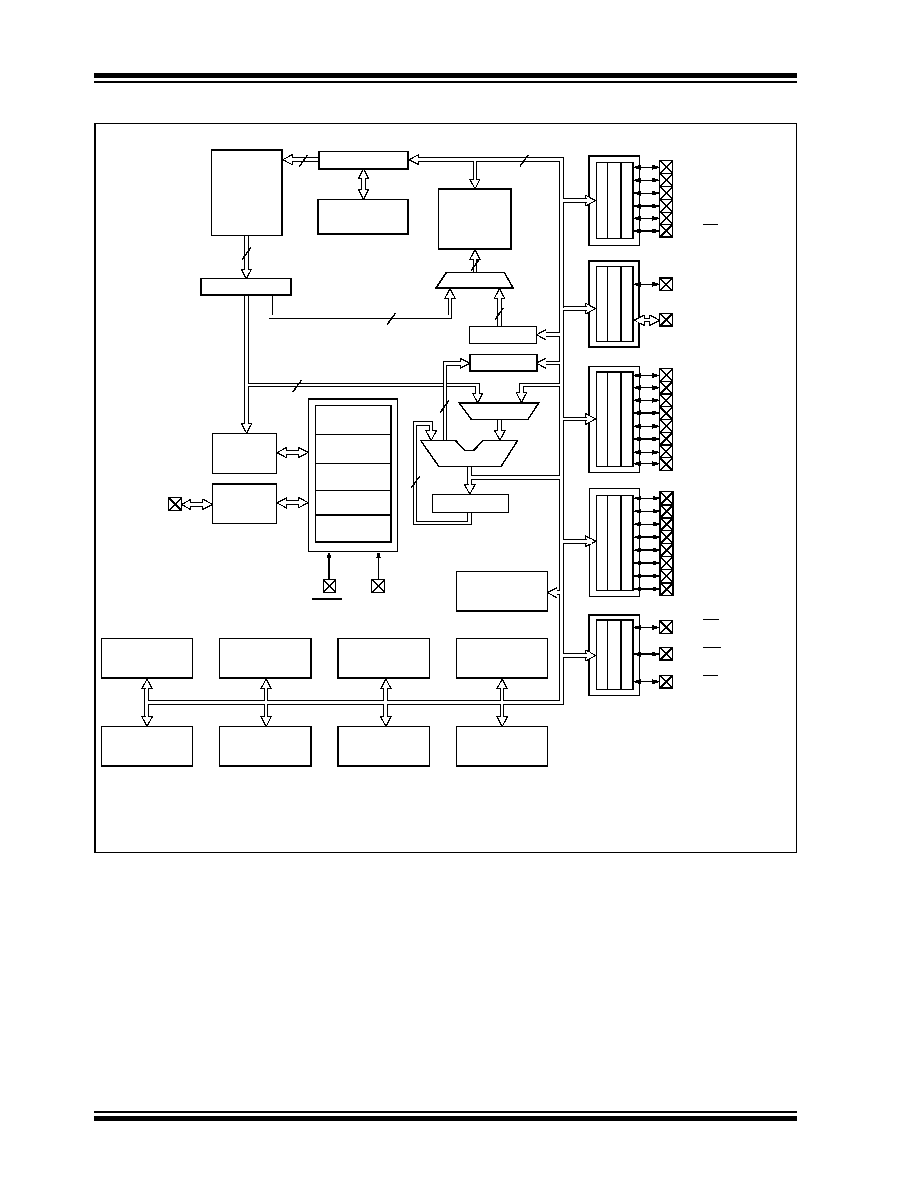

FIGURE 3-1:

PIC16C63A/65B/73B/74B BLOCK DIAGRAM

EPROM

Program

Memory

13

Data Bus

8

14

Program

Bus

Instruction reg

Program Counter

8 Level Stack

(13-bit)

RAM

File

Registers

Direct Addr

7

RAM Addr(1)

9

Addr MUX

Indirect

Addr

FSR reg

STATUS reg

MUX

ALU

W reg

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Instruction

Decode &

Control

Timing

Generation

OSC1/CLKIN

OSC2/CLKOUT

MCLR

VDD, VSS

PORTA

PORTB

PORTC

PORTD(3)

PORTE(3)

RA4/T0CKI

RA5/SS/AN4(2)

RB0/INT

RB7:RB1

RC0/T1OSO/T1CKI

RC1/T1OSI/CCP2

RC2/CCP1

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RC6/TX/CK

RC7/RX/DT

RD6/PSP6

RE0/RD/AN5(2,3)

RE1/WR/AN6(2,3)

RE2/CS/AN7(2,3)

8

Brown-out

Reset

Note

1:

Higher order bits are from the STATUS register.

2: A/D is not available on the PIC16C63A/65B.

3: PSP and Ports D and E are not available on PIC16C63A/73B.

USART

CCP1

CCP2

Synchronous

A/D(2)

Timer0

Timer1

Timer2

Serial Port

RA3/AN3/VREF(2)

RA2/AN2(2)

RA1/AN1(2)

RA0/AN0(2)

Parallel Slave Port

8

3

(3)

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD0/PSP0

RD7/PSP7

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

52559-2270

CONN FFC 22POS .5MM VERT ZIF SMD

52559-1870

CONN FFC 18POS .5MM VERT ZIF SMD

DSPIC33EP64MC506-I/PT

IC DSC 16BIT 64KB FLASH 64TQFP

52745-1896

CONN FFC 18POS .5MM R/A ZIF SMD

PIC16LC622-04/P

IC MCU OTP 2KX14 COMP 18DIP

PIC16LF84A-04/P

IC MCU FLASH 1KX14 EE 18DIP

DSPIC30F1010-30I/MM

IC DSPIC MCU/DSP 6K 28QFN

52745-1696

CONN FFC 16POS .5MM R/A ZIF SMD

相关代理商/技术参数

PIC16C63A-04I/SP

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A-04I/SS

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A04SP

制造商:MICROCHIP 功能描述:NEW

PIC16C63A-20/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A-20/SP

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A-20/SP

制造商:Microchip Technology Inc 功能描述:8 Bit Microcontroller Clock Speed:20MHz

PIC16C63A-20/SS

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C63A-20E/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT